June 20, 2014

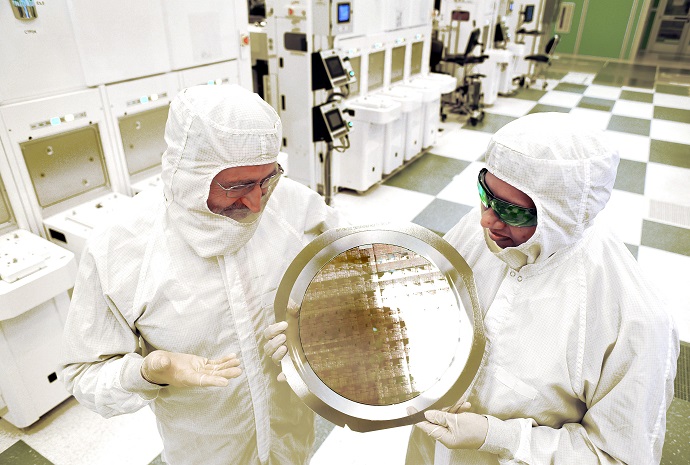

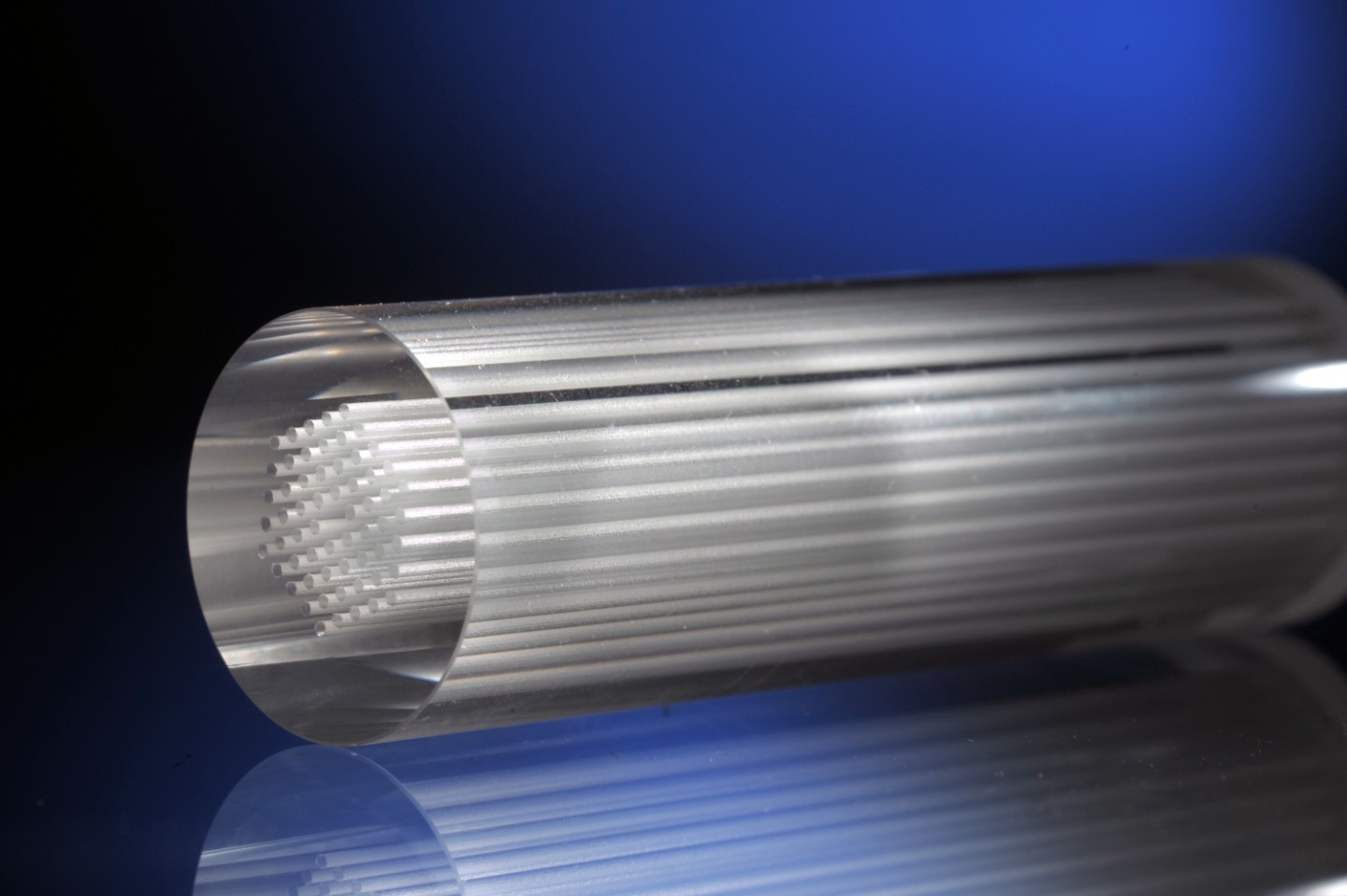

Professor Takayuki Ohba, the Tokyo Institute of Technology, ICE Cube Center, in collaboration with DISCO Corporation, Fujitsu Laboratories Ltd., PEZY Computing, and the WOW Alliance, has developed technology for the ultra-thinning process down to 4 micrometer (µm) using 300mm wafer implemented 2G bit DRAM memory. The ultra-thinning process was carried out by the bumpless WOW 3D process consist of no bumps TSV and succeeded the thickness of the 300mm silicon wafers down to 4µm, thinner than the device layer, for the first time.

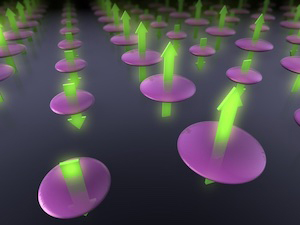

It was confirmed that there were no changes in the probability failure rate of refresh times before and after thinning-down, which means no new atomic defects occurred due to the thinning process. Using these thinned wafers, the length of the wiring between upper- and lower-layer chips is reduced to below 1/10 compared to conventional TSVs, with wiring resistance, capacitance, and volume being reduced drastically. It is expected to realize applications in ultra-small, Terabit (1 Tera is 1,000,000,000,000)-generation large-scale memory.

The results of this research were reported at the International Electron Device Meeting “VLSI Symposium 2014” held in Hawaii on June 10-13.

Source:

http://www.titech.ac.jp/english/news/2014/027995.html