Kawasaki, Japan, and Sunnyvale, CA, June 14, 2013 — Fujitsu Laboratories Limited and Fujitsu Laboratories of America, Inc. today announced the development of a clock distribution circuit that enables a 20% reduction in the power consumed by the transceiver circuits in next-generation servers that transmit data between CPUs.

In recent years, in order to improve the data processing performance of servers, in addition to improving CPU performance, there has been a need to increase the speeds at which data is transmitted between chips, such as CPUs, in a server system. On the other hand, as speeds have increased, more power is consumed by the clock distribution circuits on the transceiver circuits that transmit the data. Now, by building a tiny oscillator circuit into each transceiver and synchronizing the oscillators, Fujitsu researchers succeeded in developing a low-power clock distribution method that eliminates the need to use conventional clock distribution circuits.

It is expected that this technology will contribute to increasing the performance of the next generation of servers and supercomputers.

Details of this new technology will be presented at the 2013 Symposium on VLSI Circuits, an international conference on semiconductor circuit technology held in Kyoto beginning Tuesday, June 11, 2013 (presentation 19-2).

Background

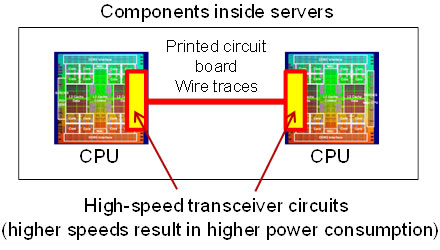

In recent years, there has been a greater need for improvements in data processing performance for servers employed in datacenters that support cloud computing. This has led to enhancements in CPU performance, as well as the development of large-scale systems that connect large numbers of CPUs. As a result, the amount of data traffic exchanged between CPUs and peripheral devices has grown substantially. To accommodate this high volume of traffic, inter-processor data communications speeds in today's servers have increased from a few Gbps to tens of Gbps. In line with faster speeds, however, power consumption has also increased. For the next generation of high-performance servers, there is an increasing need to couple higher speed with low power consumption.

Technological Challenges

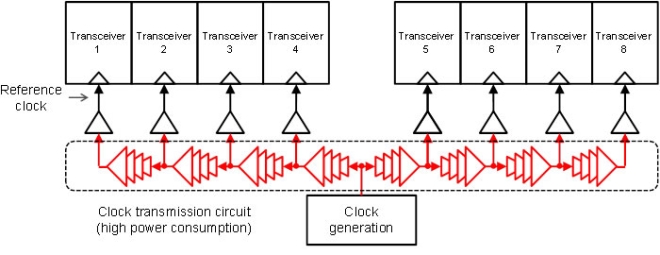

As inter-processor communications speeds have become faster between CPUs and other chips in server systems, the power consumed by transceiver circuits in transmitting the data has also increased. In particular, the proportion of the overall transceiver circuit's power consumption that is attributable to the clock distribution circuit has been growing. To make sure that the clock signal generated by the clock generator circuit is not attenuated and is able to be transmitted to each transceiver circuit, the clock distribution circuit consumes a considerable amount of power because of the relatively high signal amplification that is required over multiple stages. To achieve higher speeds with low power consumption, therefore, what has been needed is to reduce the power consumed by the transceiver circuit by developing a new, low-power clock distribution circuit.

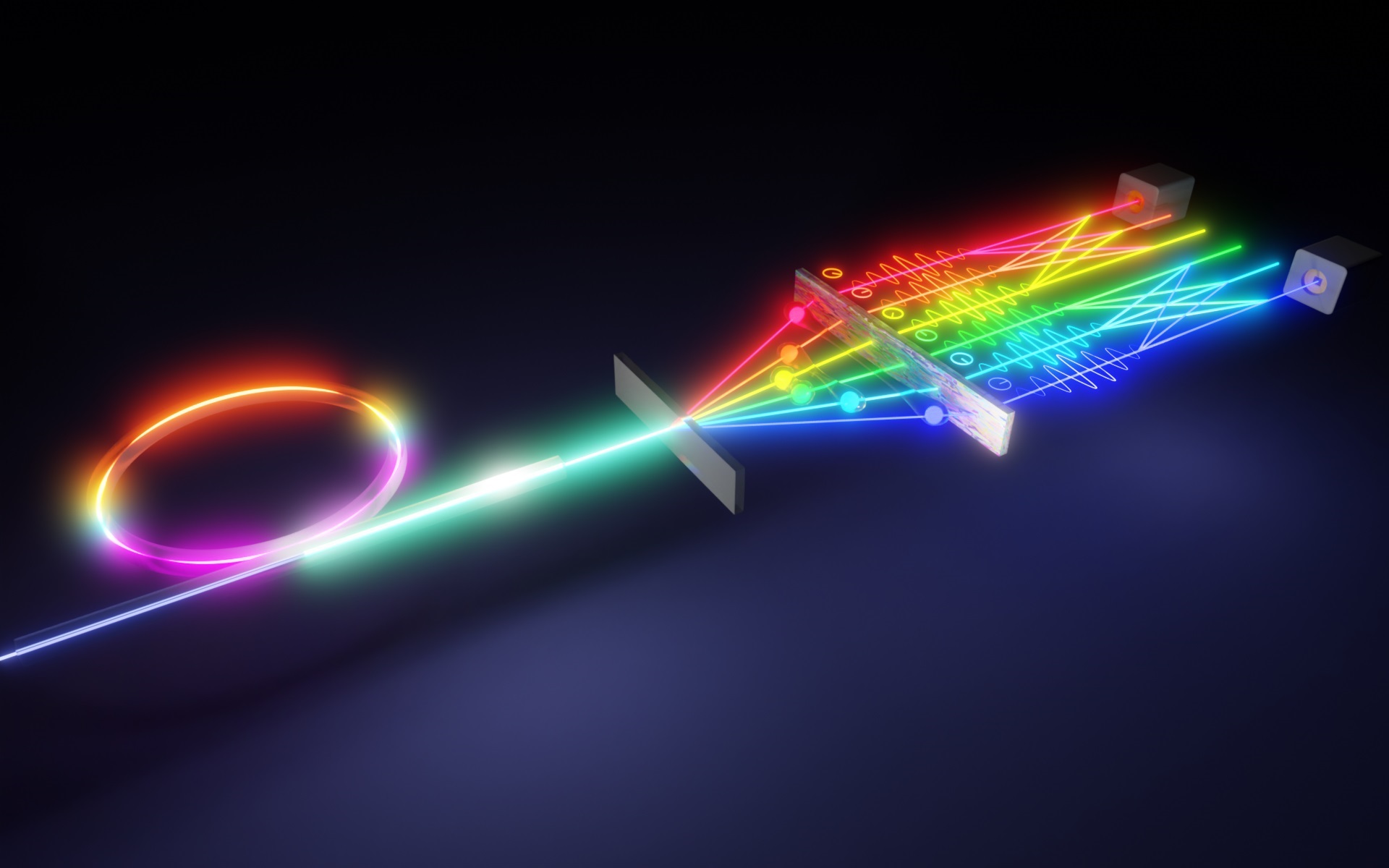

Figure 2. Conventional clock transmission method

Newly Developed Technology

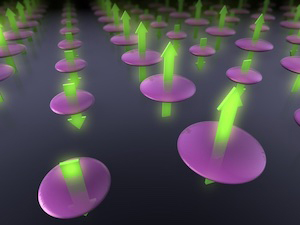

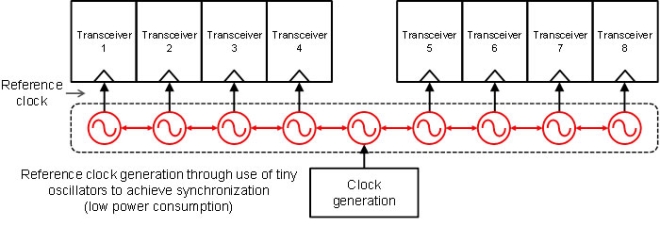

By building a tiny oscillator circuit into each transceiver and synchronizing the oscillators, Fujitsu researchers succeeded in developing a low-power clock distribution method (figure 3) that eliminates the need to use conventional clock distribution circuits.

All of the reference clocks (oscillator output) are set so that they are synchronized with the clock generator output. As a result, the frequency and phase of the reference clock for each transceiver circuit match the frequency and phase of the clock generator output. Because the signal between each oscillator required for synchronization used less amplification compared to conventional clock signal transmissions, less power is consumed.

Figure 3. New clock transmission method

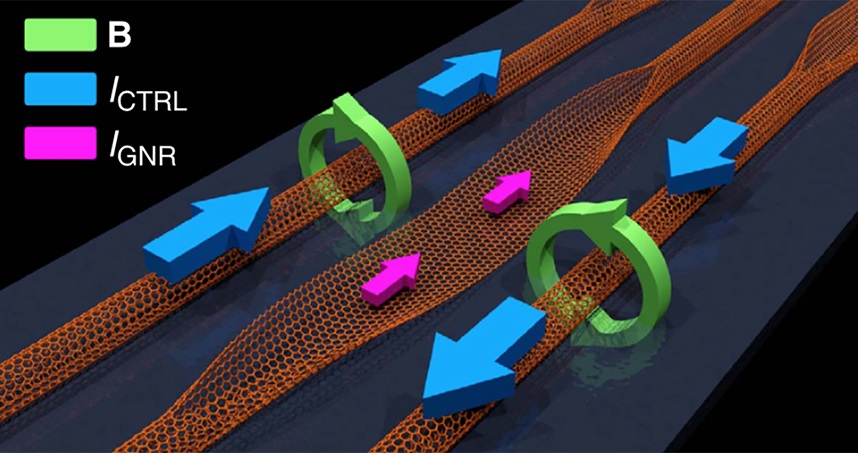

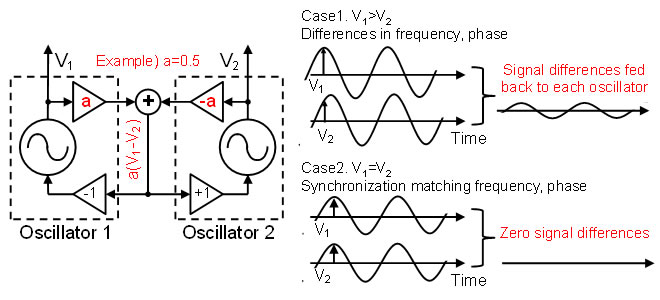

In achieving synchronization, a low amplification signal that is proportional to the amplification difference between neighboring oscillators is fed back into each oscillator (figure 4). Because this feedback is designed to drive the amplification difference to zero, ultimately the amplification difference becomes zero and the frequency and phase of the output clock for each oscillator become uniform. All neighboring oscillators are connected, with one connected to the clock generation circuit, meaning the operation of all oscillators is synchronized to the clock generation output. In this way, the generation and transmission of a low amplification differential signal enables the generation of multiple synchronized clocks.

Figure 4. Low amplification signal to synchronize each oscillator

This technology enabled a 75% reduction in the power consumed by the 16 GHz clock distribution circuit, resulting in a 20% reduction in the overall power consumed by the transceiver circuit.

Results

It is anticipated that the application of this technology will make a significant contribution to improving the performance of the next generation of servers and supercomputers.

Future Plans

Fujitsu Laboratories and Fujitsu Laboratories of America will work to apply this technology to product areas related to big data, such as the backplane interfaces that link printed circuit boards together in servers.

About Fujitsu

Fujitsu is the leading Japanese information and communication technology (ICT) company offering a full range of technology products, solutions and services. Approximately 170,000 Fujitsu people support customers in more than 100 countries. We use our experience and the power of ICT to shape the future of society with our customers. Fujitsu Limited (TSE: 6702) reported consolidated revenues of 4.4 trillion yen (US$47 billion) for the fiscal year ended March 31, 2013. For more information, please see http://www.fujitsu.com.

About Fujitsu Laboratories

Founded in 1968 as a wholly owned subsidiary of Fujitsu Limited, Fujitsu Laboratories Limited is one of the premier research centers in the world. With a global network of laboratories in Japan, China, the United States and Europe, the organization conducts a wide range of basic and applied research in the areas of Next-generation Services, Computer Servers, Networks, Electronic Devices and Advanced Materials. For more information, please see: http://jp.fujitsu.com/labs/en.

About Fujitsu Laboratories of America

Fujitsu Laboratories of America, Inc. is a wholly owned subsidiary of Fujitsu Laboratories Ltd. (Japan), focusing on research on Internet, interconnect technologies, software development and solutions for several industry verticals. Conducting research in an open environment, it contributes to the global research community and the IT industry. It is headquartered in Sunnyvale, CA. For more information, please see: www.fla.fujitsu.com.