9 September 2013

TeraSquare Inc. of Korea, one of the leading companies in fabless semiconductor development, is to unveil and demonstrate at ECOC 2013 a unique parallel CDR (Clock Data Recovery) solution which will dramatically improve signal quality across 100G systems and make massive power consumption savings in the process.

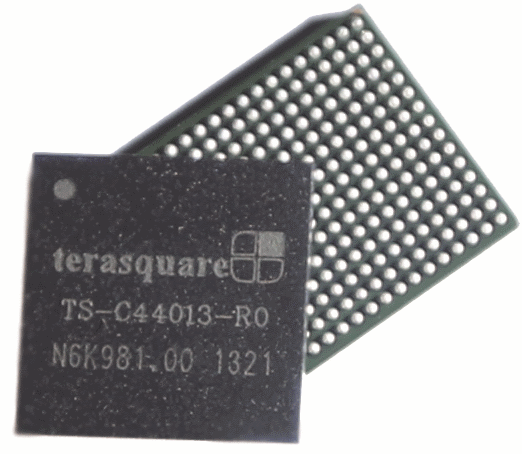

TeraSquare’s parallel CDR- TS-CM44013 slashes Integrated Chip (IC) power consumption to 0.75w compared to average CFP4 levels of 3.5w, does not require a clock reference and has built in JTOL testability- avoiding the current expensive requirement for external testing equipment.

“Our new IC is truly revolutionary and we are very excited about being able to demonstrate it at ECOC- where we will be exhibiting for the very first time” said TeraSquare CTO, Dr. Jinho Park.

“It is, by a considerable margin, the lowest power solution the market has ever seen and this critical requirement is just one of the major features that we believe will make our new development so significant across the world.”

TeraSquare’s 100Gb/s parallel CDR has 25.0-28.3Gb/s per lane in an 8mm X 8mm standard BGA package for CFP4/QSFP28 modules and supports CEI-28G-VSR specifications. Not only is the IC innovative because of its low power consumption but it features a reference-less mode and jitter filtering operation with no external filter capacitor required. The IC also includes on-chip testabilities including JTOL and PRBS generator, all of which will be demonstrated at TeraSquare’s stand at ECOC.

TeraSquare will also be introducing their second product, a 10x10Gb/s and 4x25Gb/s 100-giga reverse gearbox CDR fully supporting OIF MLG1.0/MLG2.0 and CEI-28G-VSR for CFP4/QSFP28 modules. This product has all the features of TeraSquare’s 100-giga parallel CDR (TS-CM44013) and only consumes 1.1w power. First samples will be available in February 2014.

Founded in December of 2010, TeraSquare strives to be one of the leading companies in the area of 100Gbps Ethernet IC design. Undoubtedly a promising market in the near future, the 100 Gbps Ethernet IC design is a challenging field that demands a high level of competency and capability that only a select few aspiring providers possess. With an ever-increasing demand for high speed Ethernet solutions in the IT industry, TeraSquare is gearing up to meet its goal of becoming the unparalleled provider of high speed Ethernet IC as well as other high speed ICs.

Dr. Jinho Park has over 10 years experience in low power and high-speed CMOS design and mass production. In his previous role as Senior Design Manager at Marvell in Silicon Valley, Dr. Park built and led a Research and Development group of 30 Ph.D developers which led to the analog and RF design of the world’s first 802 11ac mobile MIMO IC. With more than 40 Patents related to high-speed analog circuits and systems to his name, Dr. Park is the driving force behind turning TeraSquare’s innovative designs into competitive products.

TeraSquare has chosen the ECOC Exhibition for this global announcement because of its primary position as one of the world’s leading optical communications event. ECOC is the meeting place for everyone in the fibre optic communication and technology industry.

About TeraSquare

Founded in December of 2010, TeraSquare strives to be one of the leading companies in the area of 100Gbps Ethernet IC design. Undoubtedly a promising market in the near future, the 100 Gbps Ethernet IC design is a challenging field that demands a high level of competency and capability that only a select few aspiring providers possess. With an ever-increasing demand for high speed Ethernet solutions in the IT industry, TeraSquare is gearing up to meet its goal of becoming the unparalleled provider of high speed Ethernet IC as well as other high speed ICs. http://www.terasquare.co.kr/